Get Complete Project Material File(s) Now! »

Existing solutions for HVLP converters

As presented in the general introduction of this document, the design of the DC/DC converter with the targeted specifications is challenging. To underline the reasons why the High-Voltage Low-Power (HVLP) conversion at high-efficiency is not simple, it is interesting to look at the existing solutions with characteristics similar to the targeted specifications.

Not many HVLP DC/DC converters with specifications in the range of what is targeted with this application (i.e. few hundreds volts for the input voltage, more or less 12 V for the output voltage and a power up to few watts) can be found in literature or on the market. One reason for this is because typically a high voltage is used to transmit a high power level, hence the rare cases of high-voltage converters with such little power.

Nevertheless, few examples of isolated HVLP converters already exist, like off-line converters, which role is to transform the AC-line voltage into classical low voltage (often +5 or +12V), generally with low output power.

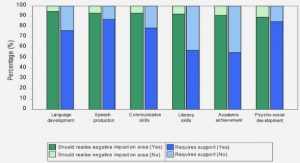

Tables 1.1 and 1.2 gather some of these solutions. Table 1.1 summarizes the important characteristics of the DC/DC converters proposed in literature. Table 1.2 gives some details about converters available on the market or proposed as a reference design. The reason for this distinction is because the information available for a product and a solution from an article are not the same. In addition, the solutions proposed in literature works are often not optimized on all the aspects, in terms of footprint for example.

Quasi-Resonant Flyback

To analyze these existing solutions, several aspects are discussed: the maximum input voltage, the efficiency, the solution’s size and the topology used.

Input voltage: Most solutions can support an input voltage up to 400 VDC, but only few of them are capable of operating for an input voltage higher than 600 V. This is because a 400 V input corresponds to the maximum DC voltage reached by the AC-line (240 VAC in Europe), with +15% additional margin for safety, that set maximum DC voltage around 390 V. Since many of these examples are intended to be used as off-line converters, they are designed to cope with maximum 400 VDC. Another reason is because the technology of the power-switches used in these converters, typically high-voltage Silicon MOSFETs, presents some limitations for the maximum voltage stress supported by the switches. Together with the Flyback topology used in many solutions, this limit of the switch technology will set the maximum input voltage close to 400 VDC.

Efficiency: The majority of DC/DC converters presented in Tables 1.1 and 1.2 do not have performances good enough to meet the targeted specifications. The only solutions presenting a satisfying efficiency are [7] and [4, 11]. But the first is a GaN-based solution, therefore not compatible with the low cost specification, while the two others operate at low switching frequency and thus requires large passive components. Most solutions have an efficiency between 65% and 80%, even though their input voltage is still quite low (< 400 V). For solutions that can support Vin > 600 V, none of them offer an efficiency higher than 65% when dealing with these voltages. This illustrates the difficulty of converting the high-voltage input into a low-voltage, low-power output with a high efficiency.

Solution size: The efficiency alone is not a good indicator, as it must also be put in line with the size of the solution. The size of the transformer is used as an indicator for the size of the overall solution, as it is usually the bulkiest component of the converter. In [3, 4, 5, 6] the transformer used is often quite small and the associated footprint on the circuit board is in the range of what is targeted for the transformer of the final solution. However, the solutions with high power [7] or high voltage [8] capabilities present a bulkier transformer. For the existing products, [2] is the only one rated for an input voltage up to 1000 V, but its module size is quite important. On the other hand, [9] that supports an input voltage up to 450 V is more compact and in the range of the targeted solution’s size.

Topology: One of the main limitations for the maximum input voltage and the efficiency is the topology used for the power-stage, which is the Flyback architecture for the vast majority of the examples. The Flyback architecture is a conventional converter topology for low-power isolated applications, but it presents some serious limits especially at high input voltage.

Limitations of the Flyback topology

The Flyback architecture is very popular because of its simplicity, its robustness and its low cost. It has a very low number of components: only one low-side power switch is required, along with one transformer and a simple diode on the secondary side, as shown in Figure 1.2 where a schematic Flyback stage is presented.

It is used in a very large panel of applications, as it can operate step-down or step-up conver-sion, thanks to the transformer turns-ratio and to its transfer function. But using this topology to operate a very high step-down might be challenging, because it is not optimized for this. This can still be useful when addressing a large input voltage range, as for [3, 2]. However, in the present application, the input voltage range is reduced, because the voltage variations on the DC bus connected to a battery are rather small and the output voltage is low, so it requires a large step-down operation. Therefore the Flyback main transfer function is not really suitable in this case.

The Flyback waveforms obtained in simulation (using the SIMetrix-SIMPLIS circuit simula-tion tool) are shown in Figure 1.3. The simulation was achieved using simplified model for the transformer and the power switches, with the input voltage equals to 400 V, the output voltage close to 12 V and the output power around 1 W.

The switching period can be divided in three steps. In the first step, the switch S is ON, a positive voltage is applied to the primary and energy is stored inside the transformer. The second step starts when the switch S turns-off. The energy stored inside the transformer is transmitted to the output, through the rectification diode D. Once the secondary current isec becomes null, the third step starts. In this last step, primary inductance Lpri and parasitic capacitors resonate, creating the sinusoidal waveforms observed on the switching node VSW and in the primary current ipri. Note that this last step only appears when the Flyback operates in Discontinuous Current Mode (DCM), which is often the case at low power.

This simple analysis of the Flyback topology and its associated waveforms already highlights several drawbacks of the topology, which will limit the capabilities and the performances of converters based on this architecture.

The first drawback relates to the voltage-stress on the primary switch S. As shown in the waveforms in Figure 1.3, a high voltage stress is applied to the switch when the current flows in the secondary side. The maximum voltage stress on S can be computed as:

VSMAX = Vin + n • Vout (1.1)

where n is the transformer turns ratio (n = Npri/Nsec) as presented in Figure 1.2.

This leads to a voltage stress on switch S that is higher than the input voltage. This is a problem when considering the design of a converter with a high input voltage (up to 1 kV). In the case of the off-line converters presented in Tables 1.1 and 1.2, it leads to choose a MOS-FET with breakdown voltage close to 600/650 V when designing a converter with maximum DC input of 400 V. This means that design for a Flyback with 500 V input voltage would require a switch with probably 800 V capability. For the case where maximum input voltage is 1 kV, this would require a device rated for 1.2 kV or higher. Such high-voltage devices exist, but they are not compatible with the low cost and integration perspectives, as they often require more complex manufacturing technologies, using wide-bandgap semiconductors like SiC.

Another issue of this architecture is the important stress on the transformer. Indeed, the core losses that occur in the magnetic core are particularly impacted by the voltage applied to the transformer. In the Flyback topology, the amplitude of the applied voltage is equal to the input voltage Vin, because the switching node is tight to the ground when switch S is ON. Hence the high losses in the magnetic device, especially when the input voltage is as high as 1 kV. Some techniques exist to mitigate these losses, like decreasing the switching frequency. However the loss reduction will only be limited and decreasing too much the switching frequency might require larger filtering components, increasing the solution size. Some applications will also put some limits on the minimum switching frequency of the converter, forbidding to get in the audio band for example (below 20 kHz). For these reasons, the high stress on the transformer in the Flyback stage will lead to high losses, preventing the converter to operate at the targeted efficiency.

Finally, the Flyback-based solutions will also present some limits due to the difficulty to operate in Zero Voltage Switching (ZVS) mode. This operating mode is used to greatly reduce the switching losses on the primary switch. Some alternatives exist to mitigate these losses in a Flyback configuration, as the quasi-resonant mode [11, 13], but it is still difficult to keep this operating mode on a large input voltage range. A more complex Flyback topology as the Active Clamp Flyback (ACF) can be used to enable the ZVS mode [3, 14], but it complicates the power-stage as it requires a second active device loosing the interest of the simplicity of the Flyback architecture.

In the end, this short analysis of the Flyback stage reveals why this topology is probably not a good candidate to design a HVLP converter with strong requirement on cost, size and efficiency.

Topology exploration

The previous overview of the Flyback topology has revealed some flaws in its characteris-tics and behavior, especially at high-voltage, making it difficult to build an efficient HVLP converter. The objective of this topology exploration is to rank different structures for the converter, in order to find those interesting in the context of the particular application at hand.

The methodology used is quite simple: using few criteria, each structure was examined to determine its expected performances when used inside a HVLP converter. Finally, the most interesting structures are compared in order to select the most suitable for the specifications and for the targeted integration technology.

The very different nature of the solutions investigated during this exploration prevent the optimization of each singular option. Therefore, to build a fair comparison without having to carefully design the power-stage of each different converter, the analysis is done qualitatively, rather than quantitatively. In other words, the aim of this exploration phase is not to design a complete (with accurate estimation of efficiency, size, etc.), but rather to study the intrinsic characteristics of each topology that transpire when analyzing its general behavior.

Table of contents :

1 Topology exploration

1.1 State of the art

1.1.1 Existing solutions for HVLP converters

1.1.2 Limitations of the Flyback topology

1.2 Topology exploration

1.2.1 Selected criteria

1.2.2 Input-Series Converters

1.2.3 Switched-Capacitor stages

1.2.4 Hybrid topologies: Multi-Level Flying-Capacitor converter

1.2.5 Comparison and selection of a candidate topology

1.3 Conclusion

2 Topology analysis

2.1 General approach

2.2 Analysis of the 2-level AHBF topology

2.2.1 Analysis of a switching period in steady-state

2.2.2 Important characteristics of the 2L-AHBF in low-power mode

2.3 Analysis of the 3L-FC-AHBF topology

2.3.1 Circuit analysis in steady-state

2.3.2 Outcomes of the switching period analysis

2.3.3 Early results from a discrete prototype

2.4 Conclusion

3 Design of an IC brick

3.1 Motivation and objectives of the IC design

3.2 Process limitations and proposed solution

3.3 Design overview

3.3.1 Power MOSFET

3.3.2 Gate-driver

3.3.3 Level-shifters

3.3.4 Active bootstrap

3.4 Conclusions on the design of the IC brick

4 Design of a transformer for HVLP converters

4.1 Selected approach for the transformer design

4.1.1 Introduction to the selected approach: Design of Experiments

4.1.2 Technological choices

4.1.3 Description of a simple model of the converter

4.2 Influence of the main design parameters

4.2.1 Example of a planar transformer design

4.2.2 Optimization of the primary inductance value in ZVS mode

4.2.3 Selection of the transformer turns ratio

4.2.4 Number of turns and balancing with frequency

4.2.5 PCB layers arrangement: mitigation of parasitic capacitors

4.2.6 Core size

4.2.7 Core material

4.3 Summary of the selected designs

4.3.1 Identifying the different types of design

4.3.2 Map of the Design of Experiments

4.4 Conclusion

5 Experimental measurements

5.1 Tests setup

5.1.1 Main board

5.2 Functional results

5.2.1 2L-AHBF configuration

5.2.2 3L-FC-AHBF configuration

5.3 ZVS mechanism and frequency optimization

5.3.1 Currents and parasitic capacitors

5.3.2 Optimization of the switching frequency

5.4 Transformer designs

5.4.1 Core material

5.4.2 Number of turns

5.4.3 Core size

5.4.4 Winding arrangement

5.4.5 Conclusion on the transformer designs

5.5 Converter performances

5.5.1 Overall results

5.5.2 Losses at high frequency

5.5.3 Comparison with state-of-art